# Source Second-Harmonic Control for High Efficiency Power Amplifiers

Masahiro Maeda, Hiroyuki Masato, Hiroyasu Takehara, Morio Nakamura, Shigeru Morimoto, Hiromasa Fujimoto, *Member, IEEE*, Yorito Ota, *Member, IEEE*, and Osamu Ishikawa, *Member, IEEE*

**Abstract**—A novel technology that drastically improves output power and efficiency of amplifiers has been developed, where source and load second-harmonic impedances, as well as the fundamental impedances, are optimally terminated in the input and output matching circuits. A record high 74% power-added efficiency (PAE) with 31.4 dBm (1.4 W) output power at a frequency of 930 MHz has been achieved as a single-stage saturated amplifier using an ion-implanted GaAs MESFET under the low supply voltage of 3.5 V. As a single-stage linear amplifier, an excellent PAE of 59% with 31.5 dBm output power has been realized at  $V_d = 4.7$  V and  $f = 948$  MHz. Saturated and linear two-stage power modules operating at 900 MHz band with 31 dBm (1.25 W) output power have been demonstrated for analog and digital cellular applications respectively, the volume of which is as small as 0.4 cc. The saturated power module has achieved a PAE of 66% at  $V_d = 3.5$  V, and the linear one has realized a PAE of 50% at  $V_d = 4.7$  V.

## I. INTRODUCTION

ADVANCED HIGH PERFORMANCE hand-held phones require high efficiency power amplifiers with a low supply voltage [1], [2]. Since the power amplifiers are the highest power consumption components in portable equipment, the efficiency is directly related to the limit on talk time or battery life. Recently, digital mobile communication systems using digital modulation signal have been growing rapidly to provide large subscriber capacities and a variety of communication services. In these systems, high efficiency linear amplifiers [3]–[5] are required instead of saturated amplifiers.

In order to obtain high efficiency, many different types of power amplifiers such as Class F and tuned Class-B have been reported [6]–[10]. In these amplifiers, load impedances for the fundamental and harmonics are optimized so as to control voltage/current waveforms applied at the output terminal of an active device. By optimally terminating the harmonics up to the second harmonic, the theoretical maximum drain efficiency is reported to be 86% [8]. In another approach, a high efficiency amplifier has been realized by inputting a quasquare voltage wave into the FET gate [11]. However, it is difficult to apply this technology to small sized power

amplifiers because the quasquare voltage wave has to be synthesized outside the amplifier.

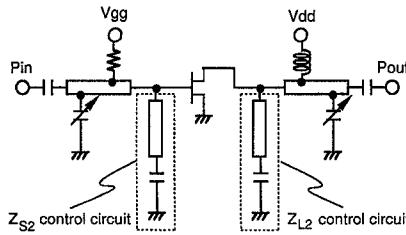

We have found that a sinusoidal voltage wave inputted into a FET gate is transformed to a quasquare wave by optimally terminating source second-harmonic impedance ( $Z_{S2}$ ) [12]. Fig. 1 shows a circuit diagram of a developed single-stage amplifier, where both  $Z_{S2}$  and load second-harmonic impedance ( $Z_{L2}$ ) can be optimally terminated with an approximate short circuit. In this paper, we describe the effects of tuning source second-harmonic impedance on output power and efficiency of GaAs MESFET's. The gate voltage and current waveforms analyzed by harmonic balance simulation are discussed. Power performance of a single-stage saturated amplifier and a two-stage saturated power module is presented in Section II. High efficiency operation of a single-stage linear amplifier and a two-stage linear power module is described in Section III.

## II. SATURATED AMPLIFIER

### A. Single-Stage Amplifier

A GaAs MESFET with a total gate width ( $W_g$ ) of 12 mm was fabricated by an ion-implantation technology. By optimizing the device dimension and the fabrication process, low knee voltage ( $V_k$ ) of I–V characteristics and high gate-to-drain breakdown voltage ( $BV_{gd}$ ) were attained [13]. The gate-source spacing ( $L_{gs}$ ), the gate length ( $L_g$ ), and the gate-drain spacing ( $L_{gd}$ ) were 0.5, 0.6, and 1.0  $\mu\text{m}$  respectively. An active channel was formed by Si ion-implantation at 80 KeV with a dose of  $3.9 \times 10^{12} \text{ cm}^{-2}$ . The gate metal was Al/Ti, and the gate region was slightly recessed. The FET had  $V_k$  of 1.2 V, and had  $BV_{gd}$  of more than 20 V at a gate current density of 1 mA/mm. The saturation drain current at  $V_g = 0$  V ( $I_{dss}$ ) and pinch-off voltage were 3.0 A and –2.8 V, respectively. This FET was assembled in a metal-based package.

In order to investigate the power performance of the FET ( $W_g = 12$  mm), an evaluation board was designed, the circuit diagram of which is shown in Fig. 1. Experimental procedures are described in the following. Source and load fundamental impedances ( $Z_{S1}, Z_{L1}$ ) are tuned with variable shunt capacitors and 50  $\Omega$  microstrip lines on the evaluation board. After their tuning is performed, source and load second-harmonic impedances ( $Z_{S2}, Z_{L2}$ ) are determined so that maximum power-added efficiency (PAE) is achieved. By varying the length of the quarter-wavelength shorted stubs

Manuscript received March 2, 1995; revised July 10, 1995.

M. Maeda, H. Masato, M. Nakamura, S. Morimoto, H. Fujimoto, Y. Ota, and O. Ishikawa are with the Semiconductor Research Center, Matsushita Electric Industrial Co., Ltd., Moriguchi, Osaka 570, Japan.

H. Takehara is with the Discrete Development Department, Matsushita Electronics Corporation, Nagaokakyō, Kyoto 617, Japan.

IEEE Log Number 9415458.

Fig. 1. Circuit diagram of the newly developed power amplifier.  $Z_{S1}$  and  $Z_{L1}$  are tuned with variable shunt capacitors and  $50\ \Omega$  microstrip lines.  $Z_{S2}$  and  $Z_{L2}$  are controlled with approximate quarter-wavelength shorted stubs.

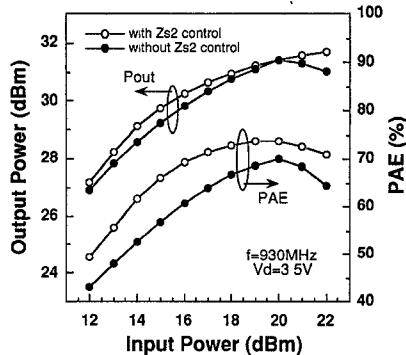

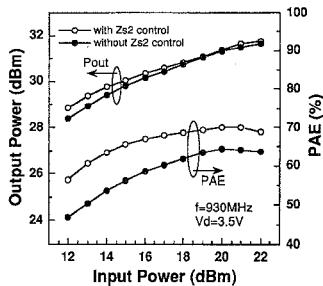

Fig. 2. Measured  $P_{out}$  and PAE of the FET at  $V_d = 3.5$  V and  $f = 930$  MHz under maximum PAE matching conditions. An excellent PAE of 74% with  $P_{out} = 31.4$  dBm at  $P_{in} = 20$  dBm is achieved under the condition of optimized  $Z_{S2}$ .

which are connected to the gate and drain electrodes on the board,  $Z_{S2}$  and  $Z_{L2}$  change around the short-circuit point along the rim of the Smith chart without affecting the values of  $Z_{S1}$  and  $Z_{L1}$ .

Power characteristics, output power ( $P_{out}$ ), and power-added efficiency (PAE) under the maximum PAE matching condition are shown in Fig. 2. Measurement was carried out at a supply voltage of 3.5 V and a frequency of 930 MHz. The drain bias current was set to be 100 mA (3% of  $I_{dss}$ ). Under the condition of optimized  $Z_{S2}$ , an excellent PAE of 74% with a  $P_{out}$  of 31.4 dBm and an associated gain of 11.4 dB is achieved at an input power ( $P_{in}$ ) of 20 dBm. A high PAE over 70% is attained over a wide input power range of 17–22 dBm. The measured values of  $Z_{S1}$ ,  $Z_{S2}$ ,  $Z_{L1}$ , and  $Z_{L2}$  for the maximum PAE were;  $Z_{S1} = 3.3 + j10.8\ \Omega$ ,  $Z_{S2} = 1.2 + j11.7\ \Omega$ ,  $Z_{L1} = 8.6 + j1.2\ \Omega$ , and  $Z_{L2} = 1.2 + j14.5\ \Omega$ . When the  $Z_{S2}$  control circuit was removed,  $Z_{S2}$  changed to  $17 + j160\ \Omega$  without affecting  $Z_{S1}$ . In such a case, maximum PAE is limited to 70%, even if matching conditions have been tuned again at the same output power of 31.4 dBm. As a result, PAE is improved by more than 4% at around the saturation output power, and by more than 8% over a lower input power range of 13–16 dBm, by optimally controlling  $Z_{S2}$ .

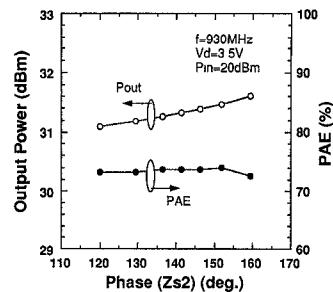

Relationship between phase angle of  $Z_{S2}$  (phase( $Z_{S2}$ )) and output performance was examined. By varying the length of the quarter-wavelength shorted stub connected to the gate terminal,  $Z_{S2}$  changes around the short-circuit point along the rim of the Smith chart. Fig. 3 shows the relationship between phase ( $Z_{S2}$ ) and output performance, where the values of  $Z_{S1}$ ,  $Z_{L1}$ , and  $Z_{L2}$  are fixed at the above mentioned

Fig. 3. Relationship between phase ( $Z_{S2}$ ) and power performance of the FET.

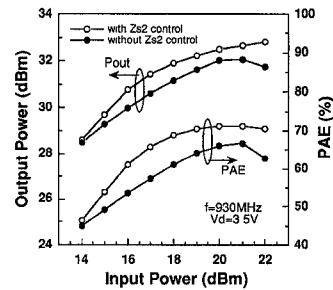

Fig. 4. Measured  $P_{out}$  and PAE of the FET under maximum  $P_{out}$  matching conditions. An increased  $P_{out}$  of 32.8 dBm at  $P_{in} = 22$  dBm with a PAE of 71% is realized under the condition of controlled  $Z_{S2}$ .

conditions. The best PAE of 74% with a  $P_{out}$  of 31.4 dBm is achieved at a phase ( $Z_{S2}$ ) of 152°, which corresponds to  $Z_{S2} = 1.2 + j11.7\ \Omega$ .

The FET was then evaluated under a matching condition for maximum output power ( $P_{max}$ ) at  $V_d = 3.5$  V and  $f = 930$  MHz. In order to increase output power,  $Z_{L1}$  was shifted to lower impedance ( $6.0 + j0.8\ \Omega$ ) than that for maximum PAE ( $8.6 + j1.2\ \Omega$ ). As shown in Fig. 4, an increased  $P_{max}$  of 32.8 dBm at  $P_{in} = 22$  dBm with a high PAE of 71% and an associated gain of 10.8 dB is achieved under the condition of controlled  $Z_{S2}$ . On the other hand,  $P_{max}$  without  $Z_{S2}$  control is limited to 32 dBm at  $P_{in} = 21$  dBm with a PAE of 67%. The FET with  $Z_{S2}$  control thus shows great improvement of maximum output power and PAE by 0.8 dB and 4%, respectively.

Harmonic balance simulation was performed on MDS (Commercial CAD by Hewlett Packard). Simulated  $P_{out}$  and PAE of the FET at  $V_d = 3.5$  V and  $f = 930$  MHz are shown in Fig. 5. By optimally controlling  $Z_{S2}$ , PAE of the FET is improved by 5% at  $P_{in} = 20$  dBm. These results which agree with the measured data confirm the advantage of the  $Z_{S2}$  control technology for obtaining high efficiency amplifiers.

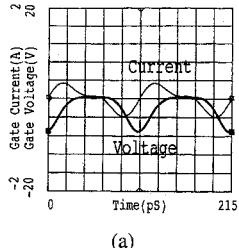

Gate voltage/current waveforms were analyzed by MDS. Fig. 6 shows simulated gate voltage/current waveforms at  $P_{in} = 20$  dBm under two conditions (with  $Z_{S2}$  control (a), and without  $Z_{S2}$  control (b)). The gate voltage waveform with  $Z_{S2}$  control (a) is close to a square wave, in comparison with that without  $Z_{S2}$  control (b). For large-signal operation, a sinusoidal wave voltage wave inputted into the gate is transformed to a quasisquare wave, by optimally terminating  $Z_{S2}$ . This quasisquare gate voltage contributes to the reduction of the voltage/current switching time at the drain. This reduces power

Fig. 5. Simulated  $P_{\text{out}}$  and PAE as a function of  $P_{\text{in}}$ . PAE is improved by 5% at  $P_{\text{in}} = 20$  dBm by optimizing  $Z_{S2}$ .

(a)

(b)

Fig. 6. Simulated Gate voltage/current waveforms at  $P_{\text{in}} = 20$  dBm under two conditions, (a) with  $Z_{S2}$  control and (b) without  $Z_{S2}$  control. The gate voltage waveform with  $Z_{S2}$  control (a) is close to a square wave.

dissipation which occurs when the drain voltage and current exist simultaneously, and results in significant improvement of PAE. In addition, the quasquare gate voltage with a wide flat portion (at  $V_g \approx 0$  V) provides a large drain current swing which is important to deliver an increased output power under limited voltage conditions.

In this simulation, the drain voltage waveform with  $Z_{S2}$  control shows a peak value of 12 V, while that without  $Z_{S2}$  control has a peak value of as low as 9 V. This indicates the new amplifier requires higher breakdown voltage ( $BV_{gd}$ ).

### B. Two-Stage Power Module

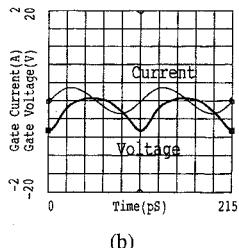

A two-stage GaAs power module for analog cellular phones was demonstrated. Fig. 7 shows a photograph of the power module. Two kinds of GaAs MESFET's (200 mW-FET for 1st-stage, 1.5 W-FET for 2nd-stage) with total gate width of 2 mm and 12 mm were used. The 1st-stage FET was plastic-molded in a surface mount type package. The 2nd-stage FET was assembled in a metal-based package, the bottom of which was soldered to the heat sink in order to decrease the thermal resistance. A semi-flexible printed board made of PPO (Poly-Phenylene-Oxide) with high  $\epsilon_r$  (10.5) and low  $\tan \delta$  (0.003) was used. The volume of the power module is 0.4 cc, which is only half of that of a conventional one [14]. The optimum

Fig. 7. Photograph of a two-stage GaAs power module, the volume of which is as small as 0.4 cc.

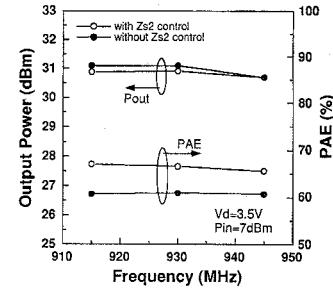

Fig. 8. Measured  $P_{\text{out}}$  and PAE of the power module. A high PAE of 66% with  $P_{\text{out}} = 31$  dBm at  $V_d = 3.5$  V is achieved over a frequency range of 915–945 MHz.

tuning of  $Z_{S2}$  is only provided with the final-stage FET, on which the efficiency mainly depends. The load second-harmonic impedance ( $Z_{L2}$ ) is also optimized in the output matching circuit in order to achieve both high PAE and low second-harmonic level.

Fig. 8 shows measured  $P_{\text{out}}$  and PAE characteristics of the power module. A high PAE of 66% with a  $P_{\text{out}}$  of 31 dBm at  $P_{\text{in}} = 7$  dBm is achieved over a frequency range of 915–945 MHz under the low supply voltage of 3.5 V. By optimally controlling  $Z_{S2}$ , PAE is improved by 6% with the same output power of 31 dBm. Supply voltage dependence of the power module was investigated. A high PAE of 66% is maintained over a supply voltage range of 2.8–3.5 V [12].

## III. LINEAR AMPLIFIER

### A. Single-Stage Amplifier

A power amplifier employed in digital cellular systems is required to operate with low distortion. This is accomplished by backing off the output power from the saturation so as

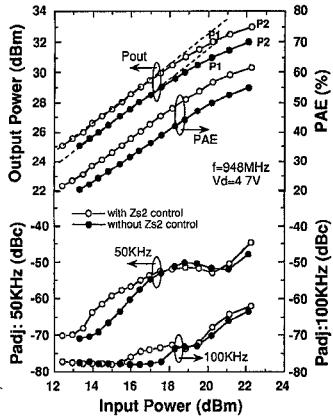

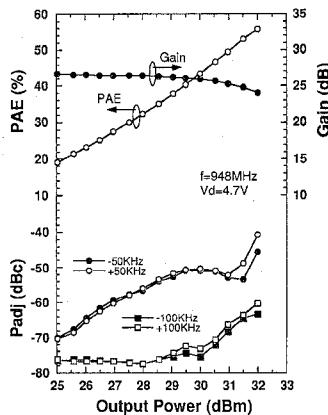

Fig. 9. Measured  $P_{\text{out}}$ , PAE and  $P_{\text{adj}}$  of the FET at  $V_d = 4.7$  V and  $f = 948$  MHz under the matching conditions for obtaining maximum  $P_{\text{out}}$  at 1 dB compression point ( $P_{-1\text{dB}}$ ).

to restrict the range of signal envelope variations. A GaAs MESFET with 30 mm gate-width ( $W_g$ ) was fabricated by the ion-implantation technology [15]. The fabrication process of this FET was basically the same as that for saturation amplifiers mentioned in Section II. The device dimensions of  $L_{\text{gs}}$ ,  $L_g$ , and  $L_{\text{gd}}$  were selected to be 1.0, 1.0, and 2.0  $\mu\text{m}$ , respectively, in order to realize low distortion properties at a supply voltage of 4.7 V. The FET ( $W_g = 30$  mm) had a saturation drain current ( $I_{\text{dss}}$ ) of 5.0 A, and a pinch-off voltage of -2.5 V. This FET was assembled in a metal-based package.

The distortion properties of the FET ( $W_g = 30$  mm) were measured on the evaluation board, the circuit diagram of which is shown in Fig. 1.  $Z_{S1}$  and  $Z_{L1}$  were tuned with variable shunt capacitors and 50  $\Omega$  microstrip lines.  $Z_{S2}$  and  $Z_{L2}$  were controlled by varying the length of the quarter-wavelength shorted stubs. An input signal was  $\pi/4$ -shift DQPSK modulation signal, and measurement was performed under the personal digital cellular (PDC) standard of Japanese digital cellular system. The calculation of adjacent channel leakage power ( $P_{\text{adj}}$ ) is described in the Appendix.

Power characteristics,  $P_{\text{out}}$ , PAE and  $P_{\text{adj}}$  under a matching condition for obtaining maximum output power at 1 dB compression point ( $P_{-1\text{dB}}$ ) are shown in Fig. 9.  $P_1$  and  $P_2$  denote  $P_{-1\text{dB}}$  and  $P_{-2\text{dB}}$  in this figure. Measurement was carried out at  $V_d = 4.7$  V and  $f = 948$  MHz. The drain bias current was set to be 350 mA (7% of  $I_{\text{dss}}$ ).  $P_{-1\text{dB}}$  with  $Z_{S2}$  control is as high as 32 dBm with a PAE of 56.5%. On the other hand,  $P_{-1\text{dB}}$  without  $Z_{S2}$  control is limited to be 31 dBm with a PAE of 50%.  $P_{-1\text{dB}}$  is increased by 1 dB with improvement of PAE by 6.5%. By using the  $Z_{S2}$  control technology, higher output power with improved PAE is realized not only in saturated region but also in linear region of amplification.

In addition, adjacent channel leakage power ( $P_{\text{adj}}$ ) with  $Z_{S2}$  control is almost the same as that without  $Z_{S2}$  control over an input power range of 18–22 dBm. The reason why  $P_{\text{adj}}$  with  $Z_{S2}$  control seems slightly greater in the linear region (input power of less than 18 dBm) is mainly because with  $Z_{S2}$  control the FET provides higher output power by almost 1 dB at the same input power.

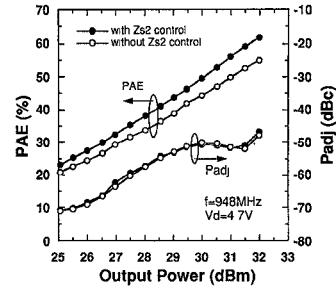

Fig. 10. Measured PAE and  $P_{\text{adj}}$  of the FET as a function of  $P_{\text{out}}$  under maximum PAE matching conditions with  $P_{\text{adj}}$  below -50 dBc at  $P_{\text{out}} = 31.5$  dBm.

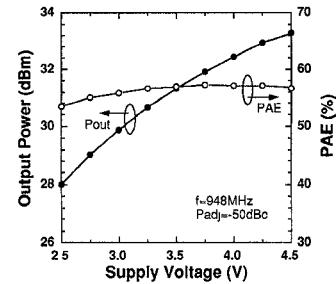

Fig. 11. Relationship between supply voltage and power performance with  $P_{\text{adj}}$  at 50 kHz offset point below -50 dBc. An excellent PAE of 57% with a  $P_{\text{out}}$  of 31.3 dBm was achieved at  $V_d = 3.5$  V.

The FET was then evaluated under maximum PAE matching condition with  $P_{\text{adj}}$  (50 kHz offset point) below -50 dBc at  $P_{\text{out}} = 31.5$  dBm. PAE and  $P_{\text{adj}}$  as a function of  $P_{\text{out}}$  are shown in Fig. 10. Under the condition of optimized  $Z_{S2}$ , an excellent PAE of 59% with an associated gain of 10.8 dB is achieved at a  $P_{\text{out}}$  of 31.5 dBm. In case without  $Z_{S2}$  control, PAE is limited to 52.5% with an associated gain of 10.4 dB. By optimally controlling  $Z_{S2}$ , PAE is improved by 6.5% at  $P_{\text{out}} = 31.5$  dBm, while  $P_{\text{adj}}$  characteristics under the both conditions agree very well over a wide output power range. A decrease in the improvement of PAE together with a decrease in the output power suggests that a voltage wave at the gate terminal could not be transformed to a quasquare wave for low output power operation although  $Z_{S2}$  was optimally terminated.

Relationship between supply voltage and power performance with  $P_{\text{adj}}$  at 50 kHz offset point below -50 dBc was evaluated under the condition of optimized  $Z_{S2}$ . The matching conditions were fixed to obtain the best performance at  $V_d = 3.5$  V. As shown in Fig. 11, an excellent PAE of 57% with a  $P_{\text{out}}$  of 31.3 dBm is achieved at  $V_d = 3.5$  V. 30 dBm (1 W) output power with a PAE of 56% is also realized at the low supply voltage of 3.0 V.

### B. Two-Stage Power Module

A two-stage GaAs power module for digital cellular phones was also demonstrated. The specification of output power of PDC handsets are 28 dBm with  $P_{\text{adj}}$  of less than -45 dBc and less than -60 dBc at 50 kHz and 100 kHz offset point from center frequency, respectively. The power module should

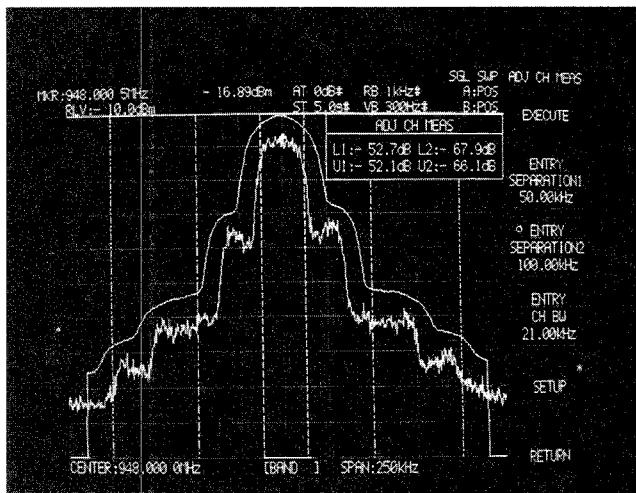

Fig. 12. Input-output properties of the power module at  $V_d = 4.7$  V and  $f = 948$  MHz. A high PAE of 50% with  $P_{out} = 31$  dBm and  $P_{adj} = -52$  dBc is achieved.

Fig. 13. The output signal spectrum of the power module at  $P_{out} = 31$  dBm and  $f = 948$  MHz.

achieve  $P_{out}$  of 31 dBm with  $P_{adj}$  of less than  $-50$  dBc and less than  $-65$  dBc at 50 kHz and 100 kHz offset point respectively, with the loss and the degradation between the power module and the antenna taken into account. The size and configuration of this power module are basically the same as that for analog cellular phones mentioned above, in which two kinds of GaAs MESFET's with total gate-width of 6 mm and 30 mm are used. The 1st-stage FET with 6 mm gate-width delivers a  $P_{out}$  of 22 dBm at  $V_d = 4.7$  V and  $f = 948$  MHz with  $P_{adj}$  of less than  $-55$  dBc at 50 kHz offset point.

Fig. 12 shows input-output properties with PAE and  $P_{adj}$  at  $V_d = 4.7$  V and  $f = 948$  MHz. Idle currents of 1st and 2nd stage FET's were set to be 80 mA and 350 mA, respectively. A high PAE of 50% with a  $P_{adj}$  of  $-52$  dBc and an associated gain of 25 dB is achieved at  $P_{out} = 31$  dBm. This PA module exhibits  $P-1$  dB and  $P-2$  dB of 30.5 dBm and 31.6 dBm, respectively. Fig. 13 shows the output signal spectrum at  $P_{out} = 31$  dBm and  $f = 948$  MHz. The upper curve in this figure is the integrated power envelope.  $L1$ ,  $U1$ ,

TABLE I

POWER PERFORMANCE OF SINGLE-STAGE

AMPLIFIERS AND TWO-STAGE POWER MODULES

|                     | Type             | $V_d$ (V) | $P_{out}$ (dBm) | PAE (%) |

|---------------------|------------------|-----------|-----------------|---------|

| Saturated Amplifier | Single-Stage     | 3.5       | 31.4            | 74      |

|                     | Two-Stage Module | 3.5       | 31              | 66      |

| Linear Amplifier    | Single-Stage     | 4.7       | 31.5            | 59      |

|                     | Two-Stage Module | 4.7       | 31              | 56      |

Note -Saturated Amplifier was measured at 930MHz.

-Linear Amplifier was measured with keeping  $P_{adj}$  of bellow  $-50$  dBc at 50KHz offset point from 948MHz

$L2$ , and  $U2$  denote  $P_{adj}$  at  $-50$  kHz,  $+50$  kHz,  $-100$  kHz and  $+100$  kHz offset point from the center frequency, respectively.

The carrier frequency range of the PDC system is from 940 MHz to 956 MHz. In this frequency range, this power module achieves a high PAE of 50% with  $P_{out} = 31$  dBm and  $P_{adj}$  of less than  $-50$  dBc at  $V_d = 4.7$  V. This value of PAE is one of the highest ever reported.

#### IV. CONCLUSION

The effects of tuning source second-harmonic impedance ( $Z_{S2}$ ) on output power and efficiency of the GaAs MESFET's have been studied at 900 MHz band. By optimally terminating source and load second-harmonic impedances ( $Z_{S2}$ ,  $Z_{L2}$ ) as well as the fundamental impedances, a record high 74% PAE with a  $P_{out}$  of 31.4 dBm (1.4 W) at 930 MHz has been achieved as a single-stage saturated amplifier using an ion-implanted GaAs MESFET ( $W_g = 12$  mm) under the low supply voltage of 3.5 V. When tuned for maximum output power, 32.8 dBm (1.9 W) output power with a PAE of 71% has been realized. As a result of harmonic balance simulation, it has been confirmed that a sinusoidal voltage wave inputted into the gate can be transformed to a quasisquare wave for large-signal operation by optimally terminating  $Z_{S2}$ .

This technology has been also useful to achieve high efficiency linear amplifiers. An excellent PAE of 59% with 31.5 dBm output power and  $P_{adj}$  below  $-50$  dBc at 50 kHz offset point has been realized as a single-stage linear amplifier using the GaAs MESFET ( $W_g = 30$  mm) at  $V_d = 4.7$  V and  $f = 948$  MHz.

Saturated and linear power modules (two-stage amplifier) have been demonstrated for analog and digital cellular applications respectively, the volume of which is as small as 0.4 cc. The saturated power module has delivered 66% PAE with a  $P_{out}$  of 31 dBm (1.25 W) over a frequency range of 915–945 MHz at  $V_d = 3.5$  V. The linear one has exhibited 50% PAE with a  $P_{out}$  of 31 dBm and  $P_{adj}$  of less than  $-50$  dBc over a frequency range of 940–956 MHz at  $V_d = 4.7$  V. The excellent performance strongly indicates the advantage of the new technology for high power and high efficiency amplifiers. The power performance of single-stage amplifiers and two-stage power modules are summarized in Table I.

## APPENDIX

$P_{\text{adj}}$  was calculated by the spectrum analyzer (Anritsu MS2602A) as follows

$$P_{\text{adj}} = 10 \log \left( \int_{Af-B/2}^{Af+B/2} p(f) df / P_{\text{total}} \right)$$

Here,

- $f$  : frequency

- $Af$  : center frequency( $Cf$ )  $\pm 50$  kHz or  $\pm 100$  kHz

- $B$  : band width of 21 kHz

- $p(f)$  : measured power at each frequency

- $P_{\text{total}}$  : total power of the spectrum

- $P_{\text{total}}$  is expressed as,

$$P_{\text{total}} = \int_{-\infty}^{+\infty} p(f) df \approx \int_{Cf-SB/2}^{Cf+SB/2} p(f) df.$$

Here,

- $Cf$ : center frequency of the signal.

- SB: band width of 250 kHz (full span of the spectrum analyzer in the measurement).

## ACKNOWLEDGMENT

The authors wish to thank M. Inada, K. Inoue, and A. Tamura for their encouragement. The authors are also grateful to M. Miura for his earnest technical assistance.

## REFERENCES

- [1] O. Ishikawa *et al.*, "Advanced technologies of low-power GaAs IC's and power modules for cellular telephones," in *IEEE GaAs IC Symp. Dig.*, 1992, pp. 131-134.

- [2] D. Ngo *et al.*, "Low voltage GaAs power amplifiers for personal communication at 1.9 GHz," in *MTT-S Int. Microwave Symp. Dig.*, 1993, pp. 1461-1464.

- [3] T. Kunihisa *et al.*, "High efficiency, low adjacent channel leakage GaAs power MMIC for digital cordless telephone," in *Proc. Microwave and Millimeter-Wave Monolithic Circuit Symp.*, 1994, pp. 55-58.

- [4] H. Ikeda *et al.*, "Phase distortion mechanism of GaAs FET power amplifier for digital cellular application," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 1992, pp. 541-544.

- [5] K. Taeoka *et al.*, "GaAs MCM power amplifier of 3.6 V operation with high efficiency of 49% for 0.9 GHz digital cellular phone system," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 1994, pp. 569-572.

- [6] M. D. Snider, "A theoretical analysis and experimental confirmation of the optimally loaded and overdriven RF power amplifier," *IEEE Trans. Electron Devices*, vol. ED-14, no. 12, pp. 851-857, Dec. 1967.

- [7] K. Chiba and N. Kanmuri, "GaAs FET power amplifier module with high efficiency," *Electron. Lett.*, vol. 19, no. 24, pp. 1025-1026, Nov. 1983.

- [8] T. Nojima *et al.*, "High efficiency microwave reaction amplifier," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 1988, pp. 1007-1010.

- [9] W. S. Kopp and S. D. Pritchett, "High efficiency power amplification for microwave and millimeter frequencies," in *MTT-S Int. Microwave Symp. Dig.*, 1989, pp. 857-858.

- [10] T. Takagi *et al.*, "A UHF band 1.3 W monolithic amplifier with efficiency of 63%," in *Proc. of Microwave and Millimeter-Wave Monolithic Circuit Symp.*, 1992, pp. 35-38.

- [11] S. Toyoda, "High efficiency single and push-pull power amplifiers," *IEEE MTT-S Int. Microwave Symp. Dig.*, 1993, pp. 277-280.

- [12] M. Maeda *et al.*, "A high power and high efficiency amplifier with controlled second-harmonic source impedance," *IEEE MTT-S Int. Microwave Symp. Dig.*, 1995, pp. 579-582.

- [13] M. Maeda *et al.*, "A 3.5 V, 1.3 W GaAs power multi-chip IC for cellular phones," *IEEE J. Solid-State Circuits*, vol. 29, no. 10, pp. 1250-1256, Oct. 1994.

- [14] Y. Ota *et al.*, "High efficient, very compact GaAs power module for cellular telephone," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 1992, pp. 1517-1520.

- [15] H. Masato *et al.*, "Analog/digital dual power module using ion-implanted GaAs MESFET's," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 1995, pp. 567-570.

**Masahiro Maeda** was born in Hyogo, Japan, on October 15, 1964. He received the B.S. and M.S. degrees in electrical engineering from Osaka Prefecture University, Osaka, Japan, in 1988 and 1990, respectively.

In 1990, he joined the Semiconductor Research Center, Matsushita Electric Industrial Co., Ltd., Osaka, Japan. He has been engaged in the research and development of the GaAs power module. He is currently engaged in development of the GaAs microwave monolithic IC's.

Mr. Maeda is a member of the Institute of Electronics, Information and Communication Engineers of Japan.

**Hiroyuki Masato** was born in Hiroshima, Japan on September 5, 1964. He was received the B.S. and M.S. degrees in electronics engineering from Hiroshima University, Hiroshima, Japan, in 1988 and 1990, respectively.

In 1990, he joined the Semiconductor Research Center, Matsushita Electric Industrial Co., Ltd., Osaka, Japan. He has been engaged in the research and development of the FET fabrication process and the crystal growth by MBE. He is currently engaged in research and development of microwave devices of the GaAs MESFET's and the HFET's.

Mr. Masato is a member of the Japan Society of Applied Physics.

**Hiroyasu Takehara** was born in Osaka, Japan, on Aug. 28, 1962. He received the B.S. and M.S. degrees in electrical engineering from Osaka Prefecture University, Osaka, Japan, in 1985 and 1987, respectively.

In 1991, he joined the Semiconductor Research Center, Matsushita Electric Industrial Co., Ltd., Osaka, Japan. He has been engaged in the research and development of the GaAs power MESFET. He is currently engaged in development of the GaAs microwave monolithic IC's.

Mr. Takehara is a member of the Institute of Electronics, Information and Communication Engineers of Japan and the Japan Society of Applied Physics.

**Morio Nakamura** was born in Kyoto, Japan, on February 3, 1968. He received the B.S. and M.S. degrees in electrical and electronics engineering from Toyohashi University of Technology, Aichi, Japan, in 1990 and 1992 respectively.

In 1992, he joined the Semiconductor Research Center, Matsushita Electric Industrial Co., Ltd., Osaka, Japan. He has been engaged in the research and development of the GaAs Power devices.

Mr. Nakamura is a member of the Institute of Electronics, Information and Communication Engineers of Japan and the Japan Society of Applied Physics.

**Shigeru Morimoto** was born in Hyogo, Japan, on October 2, 1966. He received the B.S. and M.S. degrees in electrical engineering from Tottori University, Tottori, Japan, in 1990 and 1992, respectively.

In 1992, he joined the Semiconductor Research Center, Matsushita Electric Industrial Co., Ltd., Osaka, Japan. He has been engaged in the research and development of the GaAs Power devices.

Mr. Morimoto is a member of the Institute of Electronics, Information and Communication Engineers, of Japan.

**Yorito Ota** (M'95) was born in Kobe, Hyogo, Japan, on February 23, 1960. He received the B.S. and M.S. degrees in electronics engineering from Kobe University, Hyogo, Japan, in 1982 and 1984, respectively.

In 1984, he joined the Wireless Research Laboratory, Matsushita Electric Industrial Co., Ltd., Osaka, Japan, where he has worked on AlGaAs/GaAs HBT's, using MBE growth. Since 1989, he has been engaged in the research and development of the GaAs power MESFET's and AlGaAs/GaAs power

at the Semiconductor Research Center, Matsushita Electric Industrial Co., Ltd., Osaka, Japan.

Mr. Ota is a member of the Institute of Electronics, Information and Communication Engineers of Japan and the Japan Society of Applied Physics.

**Hiromasa Fujimoto** (M'95) was born in Yamaguchi, Japan, on August 16, 1961. He received the B.S. degree in electronics engineering and M.S. degree in electrical engineering from Doshisha University, Kyoto, Japan, in 1987 and 1989, respectively.

In 1989, he joined the Semiconductor Research Center, Matsushita Electric Industrial Co., Ltd., Osaka, Japan. He has been engaged in the research and development of the GaAs fabrication process. He is currently engaged in development of the GaAs microwave monolithic IC's.

Mr. Fujimoto is a member of the Japan Society of Applied Physics.

**Osamu Ishikawa** (M'95) was born in Japan, on July 11, 1955. He received the B.S. and Ph.D. degrees in electronics engineering from Nagoya Institute of Technology, Nagoya, Japan, in 1978 and 1993, respectively.

In 1978, he joined the Semiconductor Research Center, Matsushita Electric Industrial Co., Ltd., Osaka, Japan. He has been engaged in the research and development of the power devices and low-noise devices. He is currently engaged in development of the GaAs microwave monolithic IC's.

Dr. Ishikawa is a member of the Institute of Electronics, Information and Communication Engineers of Japan.